Latch

Un latch (late memory en inglés), o coloquialmente también conocida como puerta lógica "SET" es un circuito electrónico biestable asíncrono usado para almacenar información en sistemas lógicos digitales. Un latch puede almacenar un bit de información, asimismo los latches se pueden agrupar de tal manera que logren almacenar más de 1 bit, por ejemplo el 'latch quad ' (capaz de almacenar cuatro bits) y el 'latch octal' (capaz de almacenar ocho bits). Los latches son dispositivos biestables asíncronos que no tienen entrada de reloj y cuyo cambio en los estados de salida es función del estado presente en las entradas y de los estados previos en las salidas (retroalimentación). Los latches a diferencia de los flip-flops no necesitan una señal de reloj para su funcionamiento.

Latch SR (Set-Reset)

[editar]

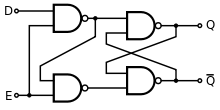

El latch lógico más simple es el SR, donde R y S representan los estados 'reset' y 'set' respectivamente. El latch es construido mediante la interconexión retroalimentada de puertas lógicas NOR (negativo OR), o bien de puertas lógicas NAND (aunque en este caso la tabla de verdad tiene salida en lógica negativa para evitar la incongruencia de los datos). El bit almacenado está presente en la salida marcada como Q, y Q´ su complementación (valor negativo a Q).

Al tener dos entradas para el ingreso de datos (S y R), tenemos 4 posibles combinaciones (recordando que 2n representa las combinaciones posibles con datos binarios, donde 'n' representa el número de bits a trabajar). Cada combinación define el estado presente en Q, de esta manera tenemos la siguiente tabla de verdad:

| Set | Reset | Q |

|---|---|---|

| 0 | 0 | Qn-1 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Indeterminado |

Cuadro 1: Tabla de la verdad para el latch SR, implementado con compuertas NOR

A partir de la información de la tabla se puede observar que cuando:

- SET=RESET=0. El latch se encuentra en su estado de reposo, y la salida Q y Q' se mantendrán en el estado que tenían antes de que se produjera esta condición de entrada.

- SET=0, RESET=1. Esta condición siempre borrara el valor presente en Q. Es decir, restablece el latch (Reset, por su palabra en inglés)

- SET=1, RESET=0. Esta condición siempre establecerá el valor de salida Q en 1. Es decir, inicializa el latch (Set, por su palabra en inglés)

- SET=RESET=1. Esta condición trata de restablecer e incializar el latch al mismo tiempo, provocando resultados inesperados. Esto debido al tiempo de propagación de las compuertas lógicas, o en su caso capacitancia parásita del circuito.

Latch D (Data)

[editar]

También conocido como latch transparente, debido a que el nivel presente en D se almacenará en el latch en el momento en que la entrada Habilitar (Enable por su palabra en inglés), sea activada, generalmente mediante un estado alto, es decir 1.

Al tener dos entradas para el ingreso de datos (EN y D), tenemos 4 posibles combinaciones (recordando que 2n representa las combinaciones posibles con datos binarios, donde 'n' representa el número de bits a trabajar). Cada combinación define el estado presente en Q, de esta manera tenemos la siguiente tabla de verdad:

| EN | D | Q |

|---|---|---|

| 0 | X | Qn-1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Cuadro 2: Tabla de la verdad para el latch D

En la primera fila de tabla se puede observar la condición EN=0 y D=X, aquí la X indica una condición no importa, en este caso cuando la entrada EN=0, el estado presente el latch será el mismo que su estado anterior sin importar el dato presente en la entrada D.

Al analizar la tabla de verdad se puede observar que cuando la entrada EN=1, el valor presente en la entrada D (1 o 0), será el valor que se mantendrá almacenado en el latch.

Adicionalmente se puede añadir (mediante el uso de una puerta lógica AND) una señal de control C para habilitar la escritura.

Véase también

[editar]Referencias

[editar]- Ronald J. Tocci, Neal S. Widmer, Gregory L. Moss (2007).Sistemas digitales: principios y aplicaciones.Pearson Educación. ISBN 9702609704, 9789702609704.

- Sistema secuencial

Enlaces externos

[editar]- Universidad de Valladolid. «Lógica secuencial, registros de desplazamiento y contadores». Consultado el 7 de octubre de 2014.