- published: 02 Jan 2024

- views: 30

-

remove the playlistCoherent Topology

- remove the playlistCoherent Topology

Fab Fox

Fab Fox is the second studio album by Fujifabric, released in 2005 on the Capitol Records label.

Track listing

Chart positions

Lovelock, Nevada

Lovelock is the county seat of Pershing County, Nevada, in which it is the only incorporated city. It is the namesake of a nearby medium-security men's prison and a Cold War-era gunnery range. Formerly a stop for settlers on their way to California and later a train depot, the town's economy remains based on farming, mining and also increasingly on tourism.

Geography

Lovelock lies in the Humboldt River Basin, very near the terminus of the river. Some twenty miles outside the town is the Lovelock Native Cave, a horseshoe-shaped cave of about 35 ft width (11 m) and 150 ft length (46 m) where Northern Paiute natives anciently deposited a number of duck decoys and other artifacts.

According to the United States Census Bureau, the city has a total area of 0.9 square miles (2.3 km2), all of it land. It has four differently designed welcome signs with pioneer and Wild West themes placed on its approach roads. At the southern end of town is the 20-acre reservation of the Lovelock Paiute Tribe.

Coherent topology

In topology, a coherent topology is a topology that is uniquely determined by a family of subspaces. Loosely speaking, a topological space is coherent with a family of subspaces if it is a topological union of those subspaces. It is also sometimes called the weak topology generated by the family of subspaces, a notion which is quite different from the notion of a weak topology generated by a set of maps.

Definition

Let X be a topological space and let C = {Cα : α ∈ A} be a family of subspaces of X (typically C will be a cover of X). Then X is said to be coherent with C (or determined by C) if X has the final topology coinduced by the inclusion maps

By definition, this is the finest topology on (the underlying set of) X for which the inclusion maps are continuous.

Equivalently, X is coherent with C if either of the following two equivalent conditions holds:

1585 Union

1585 Union (1947 RG) is a main-belt asteroid discovered on September 7, 1947, by E. L. Johnson at Johannesburg (UO).

References

Haymarket (MBTA station)

Haymarket is an MBTA subway station serving the Green and Orange lines, located at the corner of Congress and New Sudbury streets in downtown Boston, Massachusetts. Haymarket allows transfers between the Orange and Green lines, as does North Station one stop to the north. Haymarket was named for Haymarket Square, which has served as a produce market since around 1830.

Unusually, the two subway lines that converge at Haymarket are not stacked vertically underground, but instead are parallel at approximately the same level. The Orange Line access consists of two side platforms to serve the line's two tracks, while the Green Line is served by a single island platform which is divided mostly in half by a wall. Passenger transfers between lines require changing levels via stairs or elevator, so it may be preferable to transfer at more-spacious North Station, which also allows convenient cross-platform transfers for inbound trips.

The station is fully wheelchair accessible.

Referee

A referee is the person of authority in a variety of sports who is responsible for presiding over the game from a neutral point of view and making on-the-fly decisions that enforce the rules of the sport, including sportsmanship decisions such as ejection. The official tasked with this job may be known, in addition to referee, by a variety of other titles as well (often depending on the sport), including umpire, judge, arbiter, arbitrator, linesman, commissaire, timekeeper, touch judge or Technical Official (by the International Olympic Committee).

Origin

The term referee originated in association football. Originally the team captains would consult with each other in order to resolve any dispute on the pitch. Eventually this role was delegated to an umpire. Each team would bring their own partisan umpire allowing the team captains to concentrate on the game. Later, the referee, a third "neutral" official was added, this referee would be "referred to" if the umpires could not resolve a dispute. The referee did not take his place on the pitch until 1891, when the umpires became linesmen (now assistant referees). Today, in many amateur football matches, each side will still supply their own partisan assistant referees (still commonly called club linesmen) to assist the neutral referee appointed by the governing football association if one or both assistant referees are not provided. In this case, the role of the linesmen is limited to indicating out of play and cannot decide off side.

Encounter (TV series)

Encounter is a five-week anthology television series aired from Toronto, Canada, and carried by both CBC Television and ABC from October 5 to November 2, 1958. In Canada the series was known as General Motors Presents.

The one-hour dramas were either romance, adventure, or mystery stories. Patrick Macnee, Barry Morse and William Shatner were among those who appeared on Encounter.. ABC had planned to air 39 episodes of the series, but aired only 5.

In the United States, Encounter followed the western series Colt .45. The program faced competition on CBS from The Alfred Hitchcock Show and The $64,000 Question. NBC at the time aired part of The Dinah Shore Chevy Show.

It is not known what program succeeded Encounter in the 9:30 Eastern time slot beginning on Sunday, November 9, 1958. The following season The Alaskans, an adventure program set in Alaska and starring Roger Moore, Dorothy Provine, and Jeff York, aired on ABC in that time period.

Encounter is not the shortest-running series on an American television network. In the fall of 1966, The Tammy Grimes Show, a situation comedy starring Tammy Grimes, ran only four episodes on ABC before it was cancelled.100 Grand, an ABC quiz show, lasted for only three episodes after its debut in the fall of 1963 on the Sunday evening schedule. A program called Turn-On, promoted as a sophisticated answer to NBC's Laugh In, was cancelled on the air during its first and only episode.

Podcasts:

-

Optimal Coherence Topology

#education #engineeringphysics #physics #learnit #learnitofficial #onthegowisdom

published: 02 Jan 2024 -

A Temporal Coherent Topology Optimization Approach for AssemblyPlanning of Bespoke Frame Structures

We present a computational framework for planning the assembly sequence of bespoke frame structures. Frame structures are one of the most commonly used structural systems in modern architecture, providing resistance to gravitational and external loads. Building frame structures requires traversing through several partially built states. If the assembly sequence is planned poorly, these partial assemblies can exhibit substantial deformation due to self-weight, slowing down or jeopardizing the assembly process. Finding a good assembly sequence that minimizes intermediate deformations is an interesting yet challenging combinatorial problem that is usually solved by heuristic search algorithms. In this paper, we propose a new optimization-based approach that models sequence planning using a se...

published: 07 May 2023 -

Algebraic Topology: Coherent topologies | THESUBNASH - Jeden Tag ein neues Mathevideo

Diese Bücher empfehle ich fürs Studium https://amzn.to/2z8alp6 Abonniere THESUBNASH http://www.youtube.com/user/thesubnash?sub_confirmation=1 Direkt zu den Playlists: https://www.youtube.com/user/TheSubNash/playlists?flow=grid&view=1 Math Channel http://www.youtube.com/user/thesubnash?sub_confirmation=1 Neue Mathebücher der letzten 30 Tage auf Amazon.de: https://amzn.to/2O34fsi Given some topology on X an some open cover we construct the related coherent topology and look at its properties Was ist eigentlich die i-te Wurzel aus i ? Jetzt ansehen: https://www.youtube.com/watch?v=U6Csy9FfXO0

published: 02 Mar 2018 -

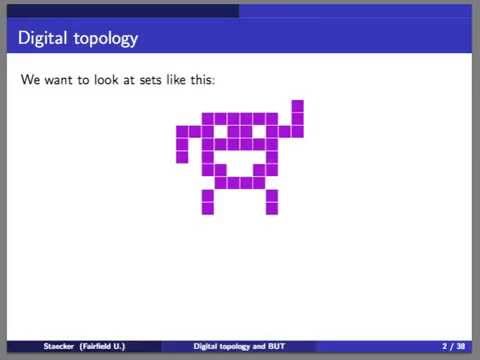

Some digital topology and a Borsuk-Ulam Theorem

A talk about digital topology and a digital Borsuk-Ulam Theorem. I gave the talk in July 2015 at the Fairfield University Math REU program colloquium. The talk should be accessible to math undergraduates and enthusiasts, even better if you have some basic topology background. Link to my digital Borsuk-Ulam paper: http://arxiv.org/abs/1506.06426 Link to Chris Staecker webarea: http://cstaecker.fairfield.edu/~cstaecker/index.html

published: 26 Jul 2015 -

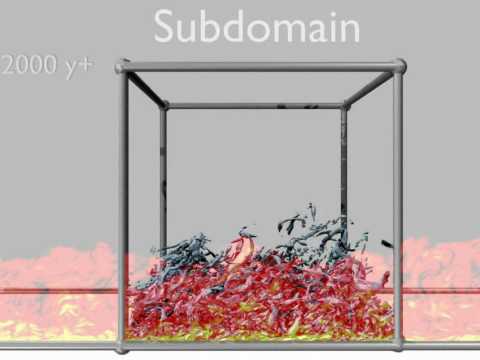

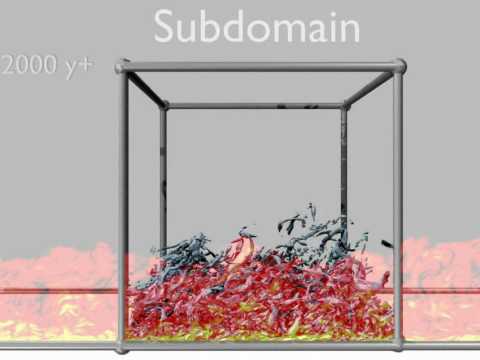

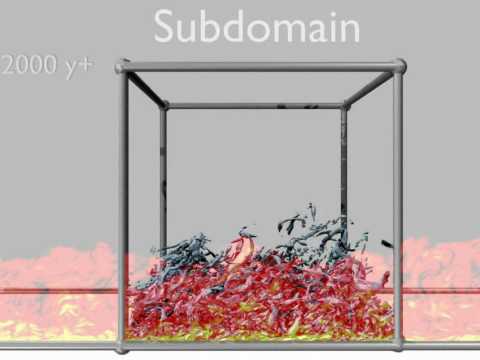

Topology, non-local geometry and dynamics of coherent structures in wall-bounded flows

This video presentation summarizes the research carried out during the 2010 Summer Program at the Center for Turbulence Research (CTR), NASA/Stanford University, by the group formed by Julio Soria, Callum Atkinson and Xiaohua Wu as visitor researchers and Sergei Chumakov and Iván Bermejo-Moreno as CTR hosts.

published: 02 Aug 2010 -

Heterogeneous Multi-processor Coherent Interconnect

In this video from the 2013 Hot Interconnects Conference, Kai Chirca presents: Heterogeneous Multi-processor Coherent Interconnect. "The rapid increase in processor and memory integration onto a single die continues to place increasingly complex demands on the interconnect network. In addition to providing low latency, high speed and high bandwidth access from all processors to all shared resources, the burdens of hardware cache coherence and resource virtualization are being placed upon the interconnect as well. This paper describes a multi-core shared memory controller interconnect (MSMC) which supports up to 12 processors, 8 independent banks of IO-coherent on-chip shared SRAM, an IO-coherent external memory controller, and high-bandwidth IO connections to the SoC infrastructure. MSMC ...

published: 28 Aug 2013 -

Algebraic Topology 20: Introduction to Cohomology

Playlist: https://www.youtube.com/playlist?list=PLOROtRhtegr7DmeMyFxfKxsljAVsAn_X4 We give a brief recap of homology and then show how dualizing the chain complex by Hom(--,Z) gives a cochain complex with coboundary maps that we use to calculate cohomology. We show that for finitely generated chain groups, we can calculate the cohomology in terms of the homology groups. Then we dualize with other coefficient groups G and discuss the universal coefficient theorem for cohomology. Presented by Anthony Bosman, PhD. Learn more about math at Andrews University: https://www.andrews.edu/cas/math/ In this course we are following Hatcher, Algebraic Topology: https://pi.math.cornell.edu/~hatcher/AT/AT.pdf

published: 28 Mar 2024 -

Oracle Coherence Data Grid

Google Tech Talks June 27, 2007 ABSTRACT Data Grid-based infrastructures are being developed, deployed and used to achieve unlimited application scalability and continuous availability. This presentation focuses on Oracle Coherence Data Grid and how it's capabilities, which includes coherent in-memory caching, dynamic data partitioning, even processing, parallel query and process execution and on how these capabilities enable achievement of these goals and more. In this presentation we will address: · How Coherence capabilities function, such as coherent in-memory caching, dynamic data partitioning, and parallel query and process execution, and how they enable a new generation of grid...

published: 09 Oct 2007 -

What is a Mesh Network? Everything You Need to Know

A mesh network, sometimes called mesh network topology, is a network that connects a group of devices to each other. Devices, also referred to as nodes, are connected in a way that some, if not all nodes, have multiple paths to other nodes. Watch to learn what a mesh network is and how it works. 🔎 Read more: What is mesh network ➡️ https://www.techtarget.com/iotagenda/definition/mesh-network-topology-mesh-network What is wireless mesh network ➡️ https://www.techtarget.com/searchnetworking/definition/wireless-mesh-network ------------------------------------------------------------------------------ 🔔Subscribe to Eye on Tech: https://www.youtube.com/@EyeonTech?sub_confirmation=1 ------------------------------------------------------------------------------ Follow Eye on Tech: ...

published: 16 Feb 2020 -

Arteris IP: A Flexible Multiprotocol Cache Coherent Network-on-Chip (NoC) for Heterogeneous SoCs

Presented by Michael Frank, Fellow and Chief Architect, Arteris IP. As AI and ML drive chip complexity, heterogeneous architectures using multiple types of processing elements are becoming a practical solution to meet processing and power requirements in systems-on-chip (SoC). This presentation describes new technology that allows processors developed with AMBA CHI, ACE and AXI interfaces to be integrated together in a single cache-coherent system. The talk includes graphical examples that highlight topology and network node configuration flexibility and the use of integrated system-level simulation to determine optimal architectures. The Linley Fall Processor Conference featured technical presentations addressing processors and IP cores for AI applications, embedded, data center, automo...

published: 01 Dec 2020

Optimal Coherence Topology

- Order: Reorder

- Duration: 0:33

- Uploaded Date: 02 Jan 2024

- views: 30

A Temporal Coherent Topology Optimization Approach for AssemblyPlanning of Bespoke Frame Structures

- Order: Reorder

- Duration: 5:08

- Uploaded Date: 07 May 2023

- views: 382

- published: 07 May 2023

- views: 382

Algebraic Topology: Coherent topologies | THESUBNASH - Jeden Tag ein neues Mathevideo

- Order: Reorder

- Duration: 8:41

- Uploaded Date: 02 Mar 2018

- views: 137

- published: 02 Mar 2018

- views: 137

Some digital topology and a Borsuk-Ulam Theorem

- Order: Reorder

- Duration: 53:56

- Uploaded Date: 26 Jul 2015

- views: 1557

- published: 26 Jul 2015

- views: 1557

Topology, non-local geometry and dynamics of coherent structures in wall-bounded flows

- Order: Reorder

- Duration: 8:15

- Uploaded Date: 02 Aug 2010

- views: 6333

- published: 02 Aug 2010

- views: 6333

Heterogeneous Multi-processor Coherent Interconnect

- Order: Reorder

- Duration: 28:13

- Uploaded Date: 28 Aug 2013

- views: 4341

- published: 28 Aug 2013

- views: 4341

Algebraic Topology 20: Introduction to Cohomology

- Order: Reorder

- Duration: 53:24

- Uploaded Date: 28 Mar 2024

- views: 4981

- published: 28 Mar 2024

- views: 4981

Oracle Coherence Data Grid

- Order: Reorder

- Duration: 56:00

- Uploaded Date: 09 Oct 2007

- views: 35903

- published: 09 Oct 2007

- views: 35903

What is a Mesh Network? Everything You Need to Know

- Order: Reorder

- Duration: 1:38

- Uploaded Date: 16 Feb 2020

- views: 86040

- published: 16 Feb 2020

- views: 86040

Arteris IP: A Flexible Multiprotocol Cache Coherent Network-on-Chip (NoC) for Heterogeneous SoCs

- Order: Reorder

- Duration: 25:29

- Uploaded Date: 01 Dec 2020

- views: 3160

- published: 01 Dec 2020

- views: 3160

Optimal Coherence Topology

- Report rights infringement

- published: 02 Jan 2024

- views: 30

A Temporal Coherent Topology Optimization Approach for AssemblyPlanning of Bespoke Frame Structures

- Report rights infringement

- published: 07 May 2023

- views: 382

Algebraic Topology: Coherent topologies | THESUBNASH - Jeden Tag ein neues Mathevideo

- Report rights infringement

- published: 02 Mar 2018

- views: 137

Some digital topology and a Borsuk-Ulam Theorem

- Report rights infringement

- published: 26 Jul 2015

- views: 1557

Topology, non-local geometry and dynamics of coherent structures in wall-bounded flows

- Report rights infringement

- published: 02 Aug 2010

- views: 6333

Heterogeneous Multi-processor Coherent Interconnect

- Report rights infringement

- published: 28 Aug 2013

- views: 4341

Algebraic Topology 20: Introduction to Cohomology

- Report rights infringement

- published: 28 Mar 2024

- views: 4981

Oracle Coherence Data Grid

- Report rights infringement

- published: 09 Oct 2007

- views: 35903

What is a Mesh Network? Everything You Need to Know

- Report rights infringement

- published: 16 Feb 2020

- views: 86040

Arteris IP: A Flexible Multiprotocol Cache Coherent Network-on-Chip (NoC) for Heterogeneous SoCs

- Report rights infringement

- published: 01 Dec 2020

- views: 3160

Fab Fox

Fab Fox is the second studio album by Fujifabric, released in 2005 on the Capitol Records label.